클럭펄스에 대하여, 플립플롭과 래치를 정리해 둔 글을 보면 이해하는데 좀 더 도움이 됩니다

https://neogul02.tistory.com/7

[Computer] NOR R-S Latch, NAND R-S Latch

동기식, 비동기식? 클럭(CLK) 신호에 의존하여 출력이 발생되는 것을 동기식 (플립플롭) 클럭(CLK) 신호에 의존하지 않고 독립적으로 출력이 발생되는 것을 비동기식 (래치) 래치(Latch) vs 플립플롭(F

neogul02.tistory.com

플립플롭(Flip-Flop)

플립플롭은 클럭(Clock) 입력을 추가하여 클럭의 상태에 따라 동작하도록 만든 동기식 저장소입니다. 이러한 구조로 인해 플립플롭은 클럭 신호의 상승 에지나 하강 에지에서만 입력을 허용하고, 클럭 신호를 기반으로 정확한 타이밍에 데이터를 처리하는 데 사용됩니다

1. R-S 플립플롭

R-S래치에 클럭 입력 게이트를 추가한 플립플롭입니다

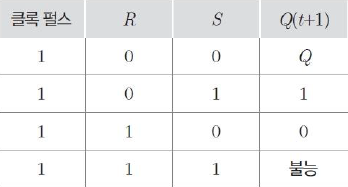

R-S 플립플롭 회로도 |

R-S 플립플롭 진리표 |

- 입력을 받는 AND 게이트 2개는 클럭이 상승 에지(=1) 일 때, 즉 A * 1 = 1 공식에 의해 값이 전달됩니다

- S와 R 모두 비활성화일 때, 즉 S=0, R=0 일 때, 현재상태를 유지(기억)합니다

- S와 R 모두 활성화일 때, 즉 S=1, R=1 일 때, 모순이 발생하여 동작에 오류가 발생합니다

이러한 문제점을 보완한 회로가 J-K플립플롭입니다

|

|

|

(4) R=1 / S=1 이면 Unknown 상태, 동작 오류 |

2. J-K 플립플롭

R-S 플립플롭에서 S=1, R=1인 경우, 불능 상태가 되는 것을 해결한 논리회로입니다

다른 모든 플립플롭들의 기능을 대용할 수 있어, 가장 널리 사용되는 플립플롭입니다

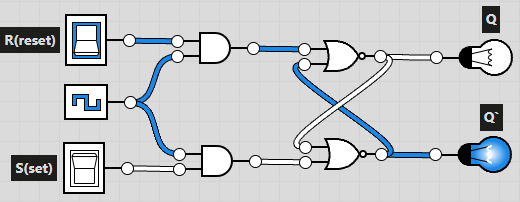

J-K 플립플롭 회로도 |

R-S 플립플롭 진리표 |

- J는 S(Set)에, K는 R(Reset)이라고 생각하면 편합니다

- S-R 플립플롭과 다르게 J=1, K=1 이 들어오면 Q는 이전 출력의 보수상태(Toggle)로 변환됩니다

|

(2) J=1 / K=0 일 때 Q=1 / Q`=0 |

(3) J=0 / K=0 일 때 (2)의 상태를 유지 |

(4) J=1 / K=1 일 때 이전상태인 (3)의 보수상태로 변환 |

3. T 플립플롭

T(Toggle) 플립플롭은 입력 신호인 T(토글)과 클럭(Clock) 신호를 갖는 순차 논리 회로이며,

J-K 플립플롭의 입력인 J와 K를 묶어서 하나의 입력 신호인 T로 동작시키는 플립플롭입니다

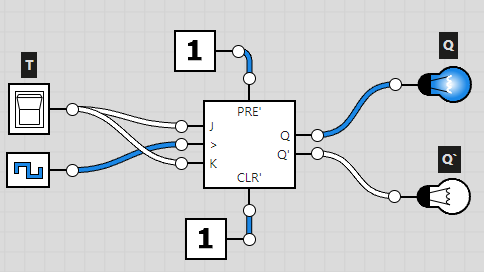

T 플립플롭 회로도 |

T 플립플롭 진리표 |

- T 플립플롭은 T가 0이면 그대로, 1이면 Q를 반대로 바꾸는 장치입니다

- T=0 이면 이전 상태의 값이 그대로 출력되고, 입력이1이면 이전 상태의 보수 상태로 출력됩니다

- J와 K를 묶어서 하나의 입력 신호인 T로 동작시키기 때문에 J-K 플립플롭으로도 표현할 수 있습니다

최초의 출력값은 Q라고 가정하고 구성했습니다

(1) 최초값을 Q=1 이라고 가정했을때, T=0 이면 이전값을 유지 |

(2) T=1 일 때 Q의 값은 반전된다 |

4. D 플립플롭

데이터(Data) 전달과 지연(Delay)을 의미해 D 플립플롭으로 불립니다

D라는 값이 입력이되면 플립플롭이 동작할때 Q 값에 D의 값이 그대로 출력됩니다

D 플립플롭 회로도 |

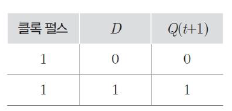

D 플립플롭 진리표 |

- D플립플롭은 입력신호 D가 변하지않고 그대로 출력되므로 D=Q의 값으로 설정됩니다

(1) D=1 일 때 Q=1 / Q`=0 |

(2) D=0 일 때 Q=0 / Q`=1 |

Logic.ly

logic.ly